February 1978

CHANGES

INTRODUCTION

## INTRODUCTION

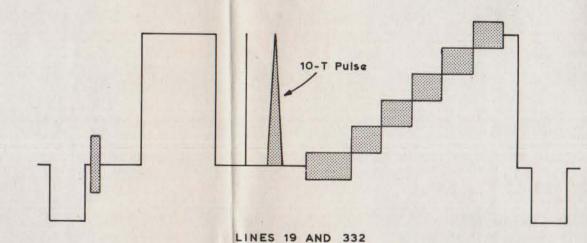

The UN20/520 forms part of an Automatic Monitor MN2/513. It accepts a gated 10-T pulse which forms part of the vertical interual test signal on lines 19 and 332. It produces a d.c. output which varies with the chrominance-luminance delay of the 10-T pulse, but is unaffected by other forms of distortion of the 10-T pulse.

The output of the UN20/520 is  $5.0 \pm 0.02$  volts for a normal 10-T input pulse.

The output varies by 1.0  $\pm$  0.02 volts for each 100 ns of chrominance-luminance delay over a range of  $\pm$  250 ns.

### CONTENTS

|                                            | Page |

|--------------------------------------------|------|

| Introduction                               | 1    |

| Recognition of distortion                  | 1    |

| Block diagram                              | 2    |

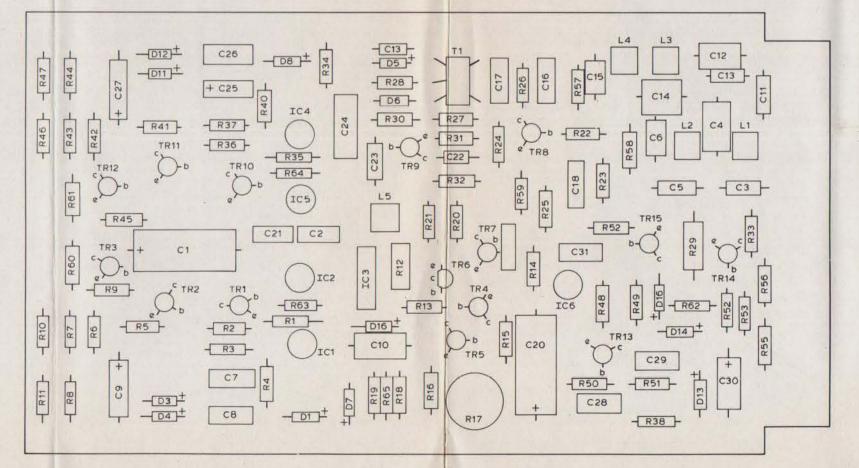

| Component layout                           | 2    |

| Typical waveforms                          | 2    |

| Alignment                                  | 3    |

| Input filtering and chrominance processing | 4    |

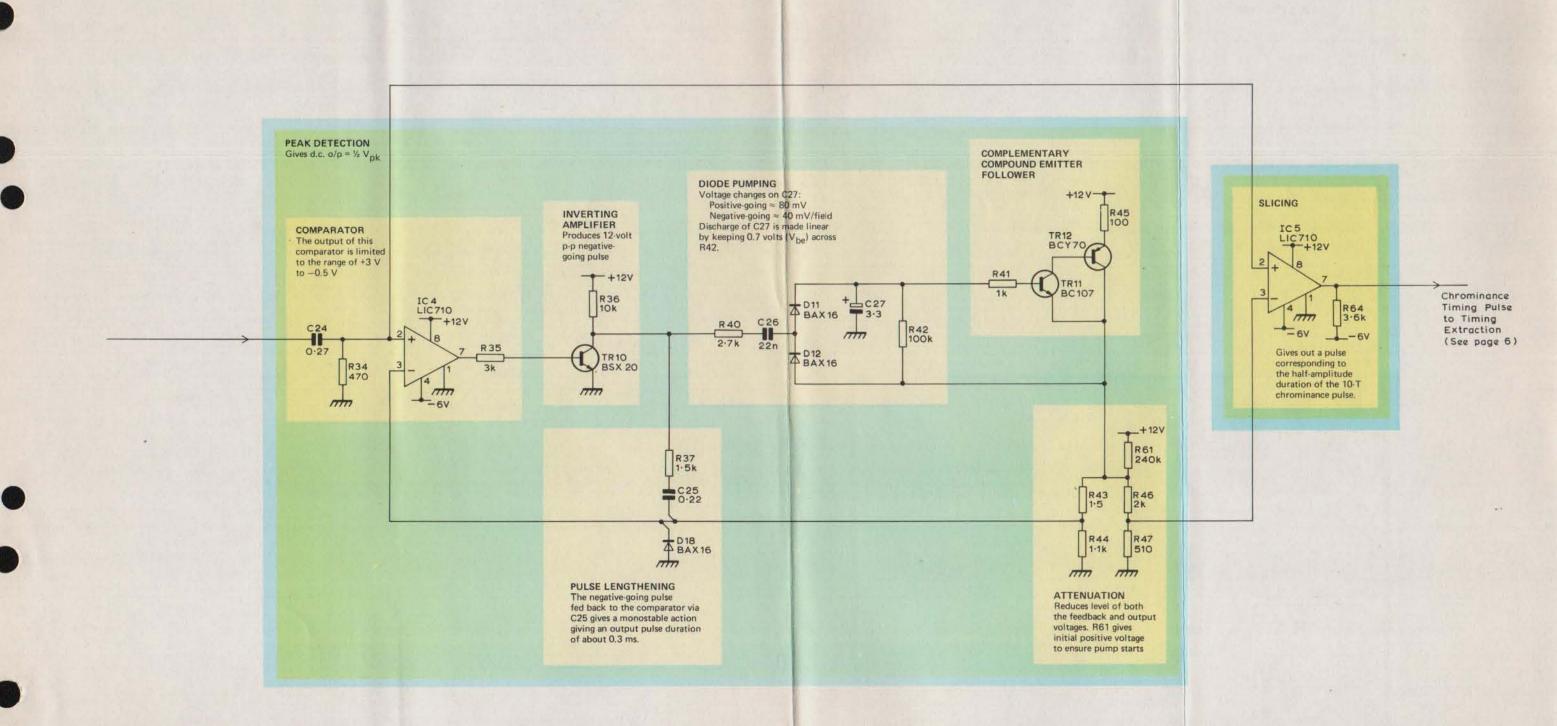

| Chrominance timing pulse generation        | 5    |

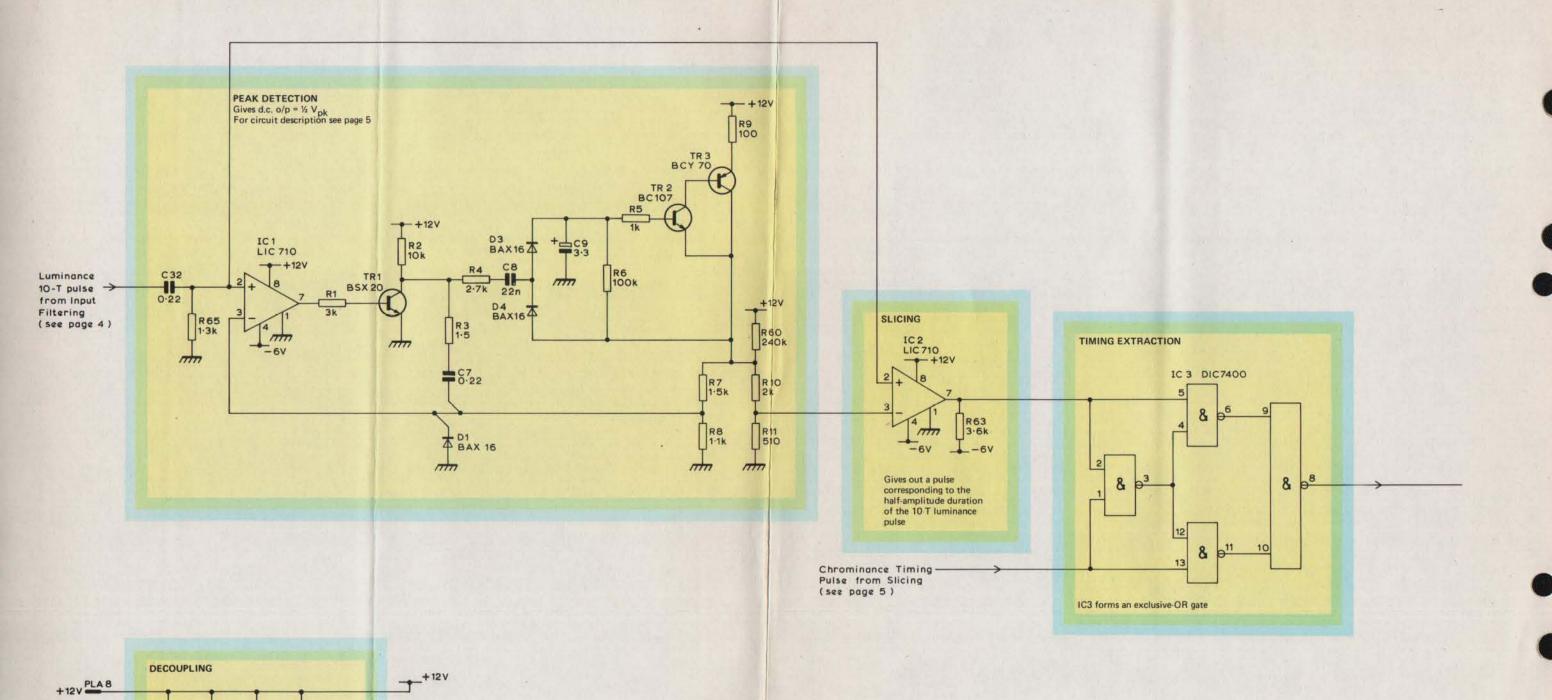

| Luminance timing pulse generation          | 6    |

| Timing extraction                          | 6    |

| Output processing                          | 7    |

|                                            |      |

### **RECOGNITION OF DISTORTION IN 10-T PULSES**

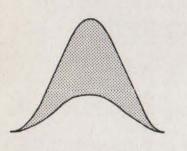

NO DISTORTION

In this 10-T pulse the chrominance and the luminance components are equal in amplitude and coincident in time. This gives a flat bottom

to the pulse.

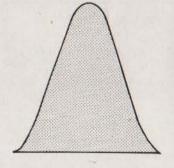

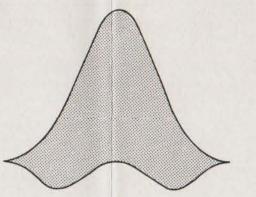

NEGATIVE C-L DELAY

In this 10-T pulse the chrominance component leads the luminance component by 200 ns.

This gives the bulge to the leading portion of the bottom of the pulse.

There is also a slight drop

in pulse height.

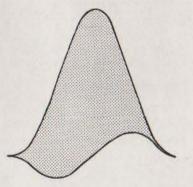

POSITIVE C-L DELAY

In this 10-T pulse the

chrominance component

lags the luminance

component by 200 ns.

This gives the bulge to the

trailing edge of the bottom

of the pulse.

There is also a drop in

pulse height.

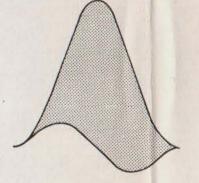

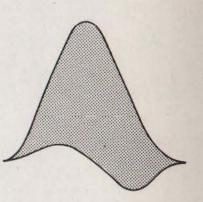

ATTENUATED

CHROMINANCE

In this 10-T pulse the

chrominance component is

attenuated by 6dB.

This reduced both the top

and bottom of the pulse by

equal amounts.

BAND-LIMITED CHROMINANCE In this 10-T pulse the chrominance component is broadened to 15-T by band-limiting.

MIXED DISTORTIONS In this 10-T pulse the distortion comprises a mixture of the previous three examples,

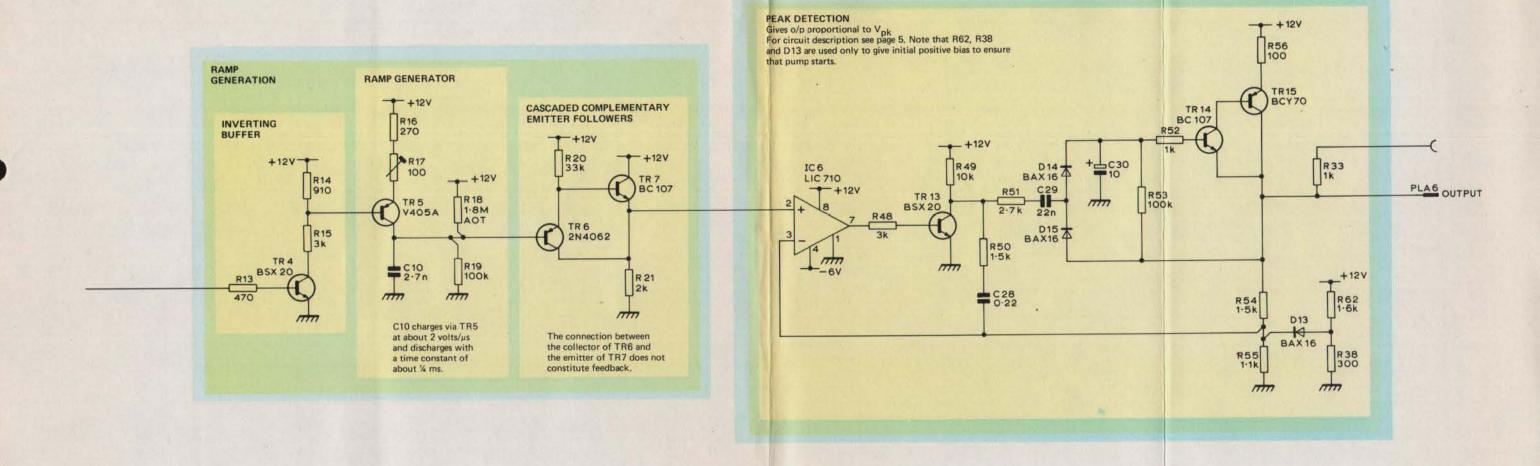

- I : Input Filtering

- II : Chrominance Processing

- III : Peak Detection

- IV : Slicing

- ▼ : Peak Detection

- VI : Slicing

- VII: Timing Extraction

- VIII: Ramp Generation

- IX : Peak Detection

- X : Decoupling

| Ref    | Type    | Base          |

|--------|---------|---------------|

| TR8.10 | BSX 20  |               |

| TR9,12 | BCY 70  | (°)           |

| TR 11  | BC 107  | D 00          |

| IC4,5  | LIC 710 | View on leads |

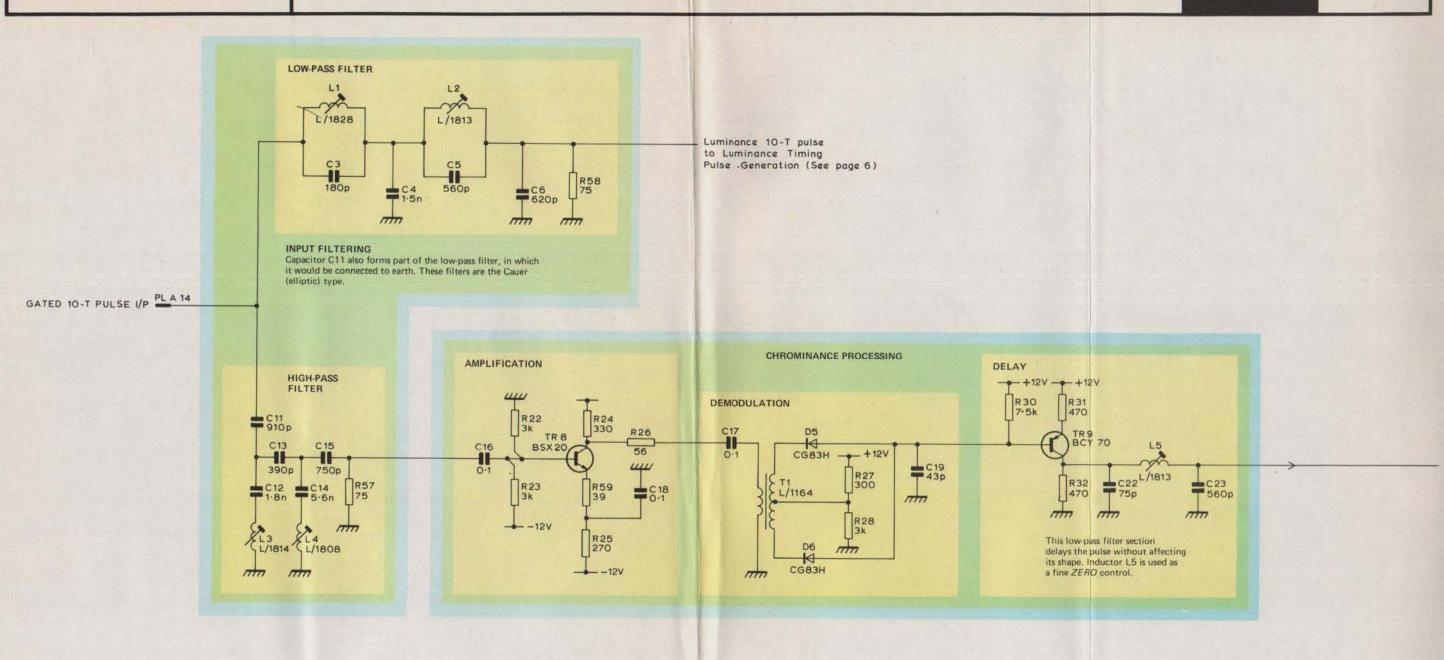

# INPUT FILTERING AND CHROMINANCE PROCESSING

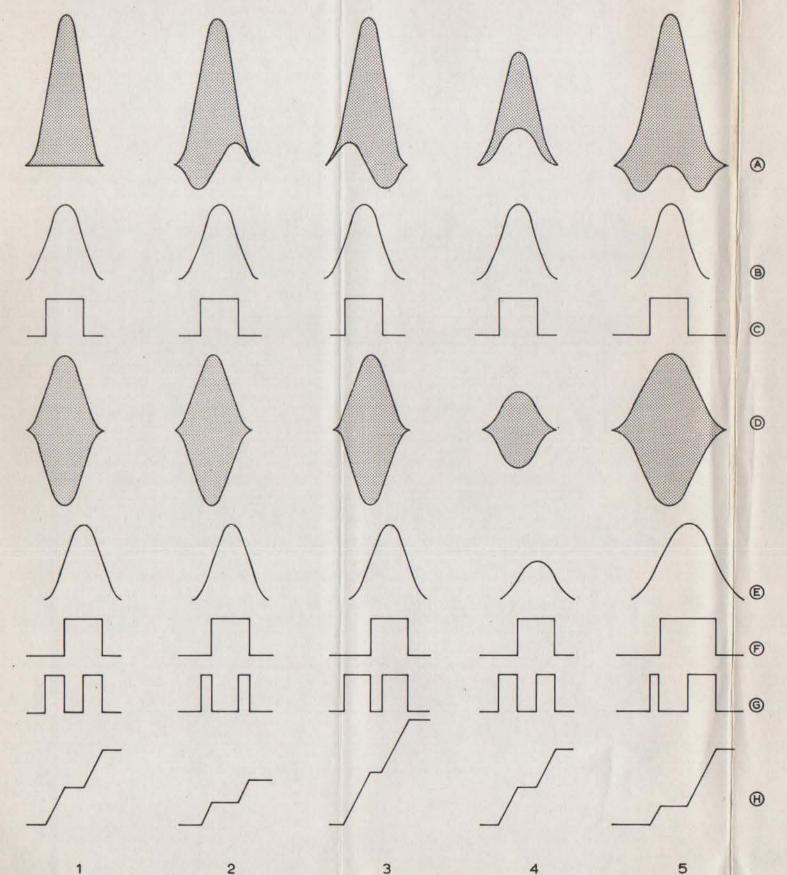

#### TYPICAL WAVEFORMS

The adjacent waveforms illustrate those found at selected points in the circuit, A - H, under various conditions of input.

CHANGES

- Normal 10-T pulse input

- 10-T pulse input with negative chrominance-luminance delay

- 10-T pulse input with positive chrominance-luminance delay

- 10-T pulse input with attenuated chrominance component

- 10-T pulse input with band-limited chrominance component. These waveforms also illustrate the circuit's independence of errors in the slicing levels

These waveforms are to be found at the following points (see page 2)

- A: Lower end of C11

- Upper end of R58

- IC 3 pin 2

- Lower end of R57

- Lower end of R34

- F: IC 3 pin 1

- IC 3 pin 8

- Lower end of R21

### ALIGNMENT

Routine alignment requires only the checking of Sensitivity and Zero adjustment. Sensitivity: Measure the output for both a normal 10-T input pulse and one with a chrominance-luminance

delay of 100 ns. The change in output should be 1.0 ± 0.02 volts. Adjust R17, with a normal input, changing the output by about twice the required change in sensitivity

Zero: With normal input and the correct Sensitivity, adjust L5 to give an output of 5.0 ± 0.02 volts d.c.

If necessary coarse adjustments can be carried out by changing the valve of R18.

Alignment of the input filters should it prove necessary is given in Designs Department Specification No. 11.90(70).

CHANGES

+5V(IC3 pin 14)

m

D16 BZY 88 C5V1

OVPLA 15

-12V PLA 10

D7 BZY88 A C6V2

> R29 200

|                                                | Semiconduc                          | tors          |

|------------------------------------------------|-------------------------------------|---------------|

| Ref                                            | Type                                | Base          |

| TR 1, 4, 13<br>TR 2, 7, 14<br>TR 3, 15<br>TR 5 | BSX 20<br>BC 107<br>BCY 70<br>V405A | 600           |

| TR 6                                           | 2N4062                              | p 0 0         |

| IC1<br>IC2<br>IC6                              | LIC 710                             | View on leads |

| IC 3                                           | DIC 7400                            | View on top   |