Issue 1 1/2/79

DESIGNS DEPARTMENT MANUFACTURING INFORMATION

No. 6.332 (78)

AUDIO DELAY UNIT

UN14/12

J.W.H. O'Clarey for Head of Designs Dept.

Written by: M.T. Ellen

Work carried out by: M.T. Ellen G. Burhop

D.N. Davison

GP

D.D.M.I. No. 6.332 (78) Title Sheet

BBC

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

DS/SPA4

## DESIGNS DEPARTMENT MANUFACTURING INFORMATION

## No. 6.332 (78)

## Audio Delay Unit UN14/12

## CONTENTS

- 1. Introduction

- 2. Specification

- 3. PRODUCTION TEST SCHEDULE

## DRAWINGS

| Circuit   |                     | D45388 | A1  |

|-----------|---------------------|--------|-----|

| Parts Lis | t                   | D45389 | A4  |

| Assembly  | and Wiring          | D45390 | A2  |

| Details   |                     | D45391 | A2  |

| P.B. No.1 | Wiring              | D45392 | A2  |

| P.B. No.1 | Wiring (Comp. side) | D45393 | A2  |

| P.B. No.1 | Comp. Location      | D45394 | A3  |

| P.B. No.1 | Drilling            | D45395 | A3  |

| P.B. No.2 | Wiring              | D45396 | A2  |

| P.B. No.2 | Wiring (Comp. side) | D45397 | A2  |

| P.B. No.2 | Comp. Location      | D45398 | A3  |

| P.B. No.2 | Drilling            | D45399 | A'3 |

|           |                     |        |     |

D.D.M.I. No. 6.332 (78) Contents Sheet

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

# No. 6.332 (78)

# Audio Delay Unit UN14/12

## 1. Introduction

This unit, which forms part of Audio Delay Equipment EP1M/23, will delay an audio signal by a preset time between 1.5 and 6m in 10 steps or between 3 and 12ms in 20 steps. It consists of two boards, one contains "bucket brigade" delay lines and the other contains a frequency synthesiser to provide the necessary clock pulses for the delay lines.

Two "bucket brigade" integrated circuits are used and each integrated circuit contains two 512 stage analogue shift registers. They are connected in a parallel/push-pull configuration to obtain optimum performance. Low pass filters with a cut off frequency of 10kHz are connected before and after the delay lines to prevent aliasing and remove sampling frequency components respectively.

The delay time is proportional to the reciprocal of the clock frequency, so by passing the output of a fixed oscillator through a programmable divider, a delay proportional to the division ratio is obtained. In order to use a low power programmable divider it is operated at a 512th of the required frequency and a phased locked loop is used to multiply its output by 512.

The delay may be set by DIC switches plugged into DIL sockets or, for more permanent installation soldered wire links. Eleven links are used and they are BCD coded such that the delay is easily related to the code number.

Pins 6 and 7 are joined so the presence of the unit may be detected. By using this facility the EP1M/23 switches to bypass if the UN14/12 is removed.

#### 2. Specification

#### Performance Data:

| Inputs: | Audio input           | Unbalanced                 |

|---------|-----------------------|----------------------------|

|         | Audio input impedance | 5KQ                        |

| •       | Audio input level     | zero programme volume      |

|         | Power consumption     | +25 + 1 volts at 60 + 10mA |

|         |                       |                            |

| Outputs: | Audio output           | Unbalanced |

|----------|------------------------|------------|

|          | Audio output impedance | <50Ω       |

| Audio | output | level |  | zero | programme | volume |

|-------|--------|-------|--|------|-----------|--------|

D.D.M.I. No. 6.332 (78) Sheet 1 of 2 sheets

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

BBC

DS/SPA4

Delay range

Delay increments

Delay tolerance

Frequency response

Gain variation with delay

Total Harmonic separation

Signal to noise ratio

1.5 to 12mS (plus delay in low pass filter)

1045 or 2045

+0.01% from 10° to 50°C

+0.5dB from 100Hz to 6.5kHz

+0.5dB from 1.5 to 12mS delay

Better than 50dB for an input signal of 1kHz at +8dBm into 6000

better than 50dB4w

#### Mechanical Data:

Chassis: CH1/65A

Indexing positions: 1,12,15

Plug Indexing positions: Al

Weight: 0.5kg

#### Installation Data:

Mount in PN3/55 and wire to pins as follows:-

1 - chassis earth

2 - audio input, balanced

3 - audio input, balanced

4 - not used

5 - not used

6 - These pins are joined in the unit and they may be used to detect

7 - that the unit is in position.

8 - not used

9 - power supply earth (0 volts)

10 - not used

11 - not used

12 - audio output (unbalanced live)

13 - audio output (earth)

14 - not used

15 - not used

16 - not used

17 - power supply positive (+25 volts)

D.D.M.I. No. 6.332 (78) Sheet 2 of 2 sheets

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

#### DESIGNS DEPARTMENT MANUFACTURING INFORMATION

## No. 6.332 (78)

## Audio Delay Unit UN14/13

## PRODUCTION TEST SCHEDULE

#### 1. Description

This unit will delay an audio signal by a preset time between 1.5 and 6ms in 10ms steps or between 3 and 12ms in 20ms steps. It consists of two boards one contains "bucket brigade" delay lines and the other contains a frequency synthesiser to provide the necessary clock pulses for the delay lines.

The frequency synthesiser should be tested first, as it is needed to drive the delay lines. It consists of a 1MHz crystal oscillator, which drives a CMOS integrated circuit that contains a divide-by-10 followed by three programmable decade dividers. The output from this divider is then multiplied by 512 by phase-locking its output with the output of a 9-bit counter. The input to the counter, which is driven from a VCO: is the required output frequency from the synthesiser.

The audio delay is provided by two "bucket brigade" integrated circuits, each of which contain two 512 stage analogue shift registers. The two shift registers within each integrated circuit are connected in a "parallel-multiplier" configuration, which means that the audio signal is alternately sampled by the two shift registers. The two pairs of shift registers are connected in a differential (push-pull) configuration, that is, they are driven in anti-phase and their outputs are summed in a differential amplifier. This arrangement provides some circuit redundancy, because if one bucket brigade I.C. fails the output only drops 6dB. Switching transients and even harmonic distortion are also minimised.

In order to obtain optimum performance from the "bucket brigade" shift registers it is necessary to drive them at the correct level, so two A.O.T. gain controls are provided. The first is used to set the "bucket brigade" input level and the other is used to adjust for OdB gain. It is also necessary to optimise the d.c. bias on the audio input to the "bucket brigade" shift registers and an A.O.T. resistor is provided for this purpose.

Low pass filters with a cut off frequency of 10kHz are connected before and after the delay lines to prevent aliasing and remove sampling frequency components respectively.

### 2. Information:

- a) Design Section:

- b) Designer:

- c) Engineer Responsible:

- d) Handbook:

- e) Technical Instruction:

- f) Other information:

- g) Pre-production batch:

Transmission Section

M.T. Ellen

D.C. Savage

Part of Handbook No. 6.163 (78) for Audio Delay Equipment EP1M/23

Not available 1.7.78

This Production Test Schedule has been tested on a pre-production batch in Designs Department.

D.D.M.I. No. 6.332 (78) Production Test Schedule Sheet 1 of 6 sheets

BBC

DS/SPA4

# Manufacturing Performance Specification

- a) Input requirements: Low distortion sine wave 20Hz to 15kHz at +10dBm max.

- b) Outputs: Similar to input but delayed by up to 12mS

- c) Power Supply: +25 + 0.5 dolts at 60 + 10mA

- d) Performance:

Gain:

0 + 0.5dB at 1kHz over full delay range

Frequency Response

+0.5dB from 100Hz to 6.5kHz

Total Harmonic separation: better than 50dB from an input signal of 1kHz at +8dBm into 6000

Signal to Noise ratio: better than 50dB4w

#### Warnings:

- a) No voltages above 50V d.c. or 30V a.e. are connected to this unit.

- b) This unit contains MOS devices. Ensure that they are not subjected to electrostatic discharges.

#### Test Apparatus Required:

1 off 0 to 30 volt variable power supply up to 100mA, fitted with an ammeter and current limit control.

1 off Frequency counter, maximum frequency > 1MHz 1 off Oscilloscope, B/W > 10MHz

2 off Oscilloscope probes

1 off A.C. Test Equipment type EP14/1

1 off A.V.O.

#### 6. Inspection:

- a) Check that the slot positions of the coding comb are correct.

- b) No mains voltages are connected to this unit. Check all the connections between PCB1 and PCB2.

- c) Check that the following components are correctly inserted.

i) Capacitors 1C1 - 1C15, 2C1 - 2C8

ii) Resistors 1R1 - 1R31, 2R1 - 1R17

Integrated Circuits 1IC1 - 1IC11, 2IC1 - 2IC4 iii)

iv) Crystal 2XL1

Plug

DIC switches vi)

> D.D.M.I. No. 6.332 (78) Production Test Schedule Sheet 2 of 6 sheets

luced or written reproduced the form without pe not the in any and Corporation drawing/specification party Corporation to a third I Broadcasting disclosed to a

#### 7. Test Procedure:

## 7.1 To check current consumption

- a) Connect the PSU (set to 0 volts) to PLA 9 (-ve) and PLA 17 (+ve). Gradually increase the voltage to 30 volts while monitoring the current.

- b) The current should increase to 60 + 10mA when the voltage reaches 18 volts and then stay constant up to 30 volts.

- c) If the current is incorrect remove the power supply link to PCB 2 and repeat the test. For this test the current should be 55 + 10mA, if so the fault is on PCB 2 otherwise it is on PCB 1.

## 7.2 To check crystal oscillator

- a) Connect the frequency counter and the oscilloscope to 2IC 1 pin 1. Measure the frequency and amplitude of the waveform.

- b) The frequency should be 1MHz + 100Hz and the waveform should be an approximately square wave between 0 and +15 volts.

- c) If the frequency is wrong check the crystal, 2C1 and 2C2. If the amplitude is wrong check 2IC2.

#### 7.3 To check variable divider

- a) Connect the frequency counter and the oscilloscope to 2IC1 pin 23. Measure the frequency and shape of the waveform with the switch settings shown in section b.

- b) The waveform should be a positive pulse (+15 to 0 volts) with a duration of 145 i.e. one cycle of the input waveform.

The frequencies should be as follows:

#### Table 1

| H | undr |   | Tens |   |      |   | Units |   |       | Frequency Hz |                 |

|---|------|---|------|---|------|---|-------|---|-------|--------------|-----------------|

|   | 12   |   | 9    |   |      | 6 | 4     |   | 2     |              | 1 Loquottoy IIa |

| 1 | 0    | 0 | 0    | 0 | 0    | 0 | 0     | 0 | 0     | 0            | 250             |

| 0 | 1    | 0 | 0    | 0 | 0000 | 0 | 0     | 0 | 00000 | 0            | 500             |

| 0 | 0    | 1 | 0    | 0 | 0    | 0 | 0     | 0 | 0     | 0            | 1000            |

| 0 | 0    | 0 | 1    | 0 | 0    | 0 | 0     | 0 | 0     | 0            | 1250            |

| 0 | 0    | 0 | 0    | 1 | 0    | 0 | 0     | 0 | 0     | 0            | 2500            |

| 0 | 0    | 0 | 0    | 0 | 1    | 0 | 0     | 0 | 0     | 0            | 5000            |

| 0 | 0    | 0 | 0    | 0 | 0    | 1 | 0     | 0 | 0     | 0            | 10000           |

| 0 | 0    | 0 | 0    | 0 | 0    | 1 | 1     | 0 | .0    | 0            | 5555.6          |

| 0 | 0    | 0 | 0    | 0 | 0    | 1 | 0     | 1 | 0     | 0            | 7142.9          |

| 0 | 0    | 0 | 0    | 0 | 0    | 1 | . 0   | 0 | 0     | 0            | 8333.3          |

| 0 | 0    | 0 | 0    | 0 | 0    | 1 | 0     | 0 | 0     | 1            | 9090.9          |

| 0 | 0    | 1 | 0    | 1 | 0    | 1 | 0     |   | 0     |              | 666.7           |

| 1 | 1    | 0 | 0    | 0 | 0    | 0 | 0     | 0 | 0     | 0            | 166.7           |

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

BBC

Production Test Schedule Sheet 3 of 6 sheets

D.D.M.I. No. 6.332(78)

c) If there is no output waveform check 2IC1. If the frequencies are wrong check that the switches change the logic levels on the "jam" inputs of 2IC1.

## 7.4 To check the VCO and 9/10 bit divider

- a) Short 2IC4 pin 9 to 0 volts then connect the frequency counter and oscilloscope to 2IC3 pin 10 and pin 14 in turn. Set U-Link to 6mS. Check the frequency and amplitude of the waveform at both points. Remove the short.

- b) The waveform at both points should be a square wave between 0 and +15 volts. The frequency at pin 10 should be 110 + 20kHz. The frequency at pin 14 should be a 512th of the frequency at pin 10. Set the U-link to 12mS. The frequency at pin 14 should now be a 1024th of the frequency at pin 10.

- c) If the amplitude of the waveform is wrong check 2IC3 and 2IC4. If the frequency at pin 10 is wrong check 2R16, 2R17 and 2C7. If the division ratio is not 512/1024, check 2IC3.

## 7.5 To check the phase locked loop

- a) Connect the frequency counter to 2IC2 pin 6.

Set the switches to the positions shown in the last two lines of table 1 and set the 'U' link to 6mS (section 7.3), in turn.

Check the frequency for each setting.

- b) The frequencies should be 682667 + 68Hz and 170667 + 17Hz respectively.

- c) If one frequency is incorrect the VCO range may need adjustment (see section 7.6). If both frequencies are incorrect check the loop filter components 2R13, 2R14 and 2C3 as well as the phase detector 2IC4.

# 7.6 To check the VCO range and loop stability

- a) Connect the oscilloscope to the VCO control input 2IC4 pin 9 and measure the voltage with the switches set as in section 7.5.

- b) Both voltages should be within the range +1 volts to +12 volts. The voltage levels will take up to 5 seconds to settle but after this time there should be negligible a.c. ripple.

- c) If one of the voltages is incorrect 2R6 should be adjusted to bring the voltages well within the specified range. If the d.c. voltage has an undamped a.c. ripple superimposed on it, check the loop filter components.

# 7.7 To check the frequency response

- a) Set the switches to the settings shown in the last two lines of table 1 (section 7.3), in turn. Connect the A.C. Test Set oscillator (600Ω source, internal 600Ω termination and OdBm) to pins 2 and 3. Connect the A.C. Test Set detector (high impedance, mean indication) to pins 12 and 13. Measure the frequency response.

- b) The gain should be constant within +0.5dB from 100Hz to 6.5kHz. The loss should be greater than 20dB at 15 and 10KHz relative to the level at 1kHz.

D.D.M.I. No. 6.332 (78) Production Test Schedule Sheet 4 of 6 sheets

BBC

c) If the frequency response is incorrect check the input and output active filter components. Also, use a high impedance probe to check the response at the output of each operational amplifier in order to isolate the fault.

#### 7.8 To check the distortion

- a) Leave the equipment set up as in section 7.6 but increase the output from the oscillator to +8dBm and set it to 1kHz. Press the "mean" button and adjust the attenuator setting to obtain a centre reading on the meter. Then press the "1kHz harmonic" button and readjust the attenuator to obtain a centre reading. Note the difference between the two attenuator settings.

- b) The difference should be greater than 50dB for both delay settings.

- c) If this test does not meet the specification go to section 7.9 otherwise go to section 7.11.

# 7.9 To set the d.c. bias level (only if unit has failed section 7.8)

- a) Leave the equipment set up as in section 7.8 but increase the output from the oscillator until clipping occurs on the UN14/12 output (use the oscilloscope to view the waveform). Adjust 1R12 to obtain equal clipping on positive and negative peaks.

- b) The clipping should only appear at an input level greater than +11dBm.

- c) If clipping occurs at a lower level it could be due to the two "bucket brigade" IC's (1IC4 and 1IC5) requiring very different bias levels. Therefore view the outputs from 1IC4 and 1IC5 to check that they limit at approximately the same input level and if they do not adjust 1R12 to a compromise setting.

# 7.10 To set the input gain control (only if unit has failed section 7.8)

- a) Repeat section 7.8 but adjust 1R7 to reduce the harmonic separation.

- b) Set 1R1 for a 51 + 1dB harmonic separation.

- c) If this figure cannot be obtained check the other amplifier stages.

# 7.11 To set the output gain control

- a) Set up the equipment as in section 7.6 and adjust 1R30 to set the output level.

- b) The output level should be 0 + 0.5dBm for both delay settings (i.e a gain of 0 + 0.5dBc.

- c) If 1R30 requires a very large adjustment 1IC4 or 1IC5 are probably faulty, resulting in excessive input attenuation to obtain the required distortion.

# 7.12 To measure the signal to noise ratio

a) Leave the equipment set up as in 7.11 and press the TPM button. Check that the TPM indicates 4 when the attenuator is a OdB. Replace the

D.D.M.I. No. 6.332 (78) Production Test Schedule Sheet 5 of 6 sheets

BBC

oscillator with a 6000 resistor, press the "weighted" button and readjust the attenuator to make the TPM peak to 4. Note the new attenuator setting.

- The reading should be better than 50dB (i.e. 50dB4w)

- If this figure cannot be obtained 1IC4 or 1IC5 are probably faulty.

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

DS/SPA4

D.D.M.I. No. 6.332 (78) Production Test Schedule Sheet 6 of 6 sheets

38 5 4 ISS.

CHANGE C'C'T REF. DESCRIPTION BBC REF. OR DRG. No. OFF No. DRAWING NUMBERS CIRCUIT 14538841 PARTS LIST 04538944 ASSY & WIRING 04539042 04539142 P. B WIRING NOI 0 4 5 3 9 2 4 2 " " (COMP SIDE) 045393 42 P.B Nº / COMP LOC 0 4539443 " " DRILLING 0 4 5 3 9 5 4 3 P.B WIRING NO2 045396A2 " " (COMP SIDE) 0 45397 42 P. B Nº 2 COMP LOC 0 4539843 " " DRILLING 1 45399 43 FURTHER INFORMATION REQUIRED FOR MANUFACTURE ASSY INFORMATION E.A 10484 WIRING INFORMATION E.A 10140 CHASSIS, CHI/6SA, TO BE MODIFIED BY CONTRACTOR AS FOLLOWS :-FRONT PANEL 04539142 DET 1 CODING PLATE DET 3 HANDLE DET4 2 PRINTED BOARD NO! 04539242, 045393A2 045394 43, 04539543 3. PRINTED BOARD Nº2 A45396A2, B45397A2. 045398 43 , 045399 43.

Broadcasting Corporation and may not be reproduced or drawing/specification is the property of the British in any form without the written disclosed to a third

4 5

6

8 9

10

12

13

14.

12

BBC UN14/12 , PARTS LIST AUDIO DELAY UNIT. DS/PLA4

SCREW, M2.5 x 619 PAN HO MS Zn P

IC SOCKET, 8 PIN, TEXAS TYPE 093082.

LINK , FREE MINIATURE , SHORTING , RED .

SOCKET, FIXED SINGLE POLE MINIATURE

DRN. K. TURNER DESIGNS DEPARTMENT.

TPD. CKD. APPD.

D45389A4 SHEET I OF 8 SHEETS

Lk \$2 | 5-23790 - 0223319.

5-27611 - 0236252

THROUGH HOLE PLATED BOARD, ALL LEADS PASSING THROUGH BOARD NOT TO BE BENT AFTER ASSEMBLY

CAUTION CMOS IC DEVICES FITTED, HANDLE WITH CARE. SEE EA10140 NOTE 14.

#### NOTES

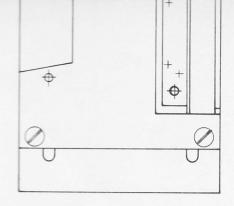

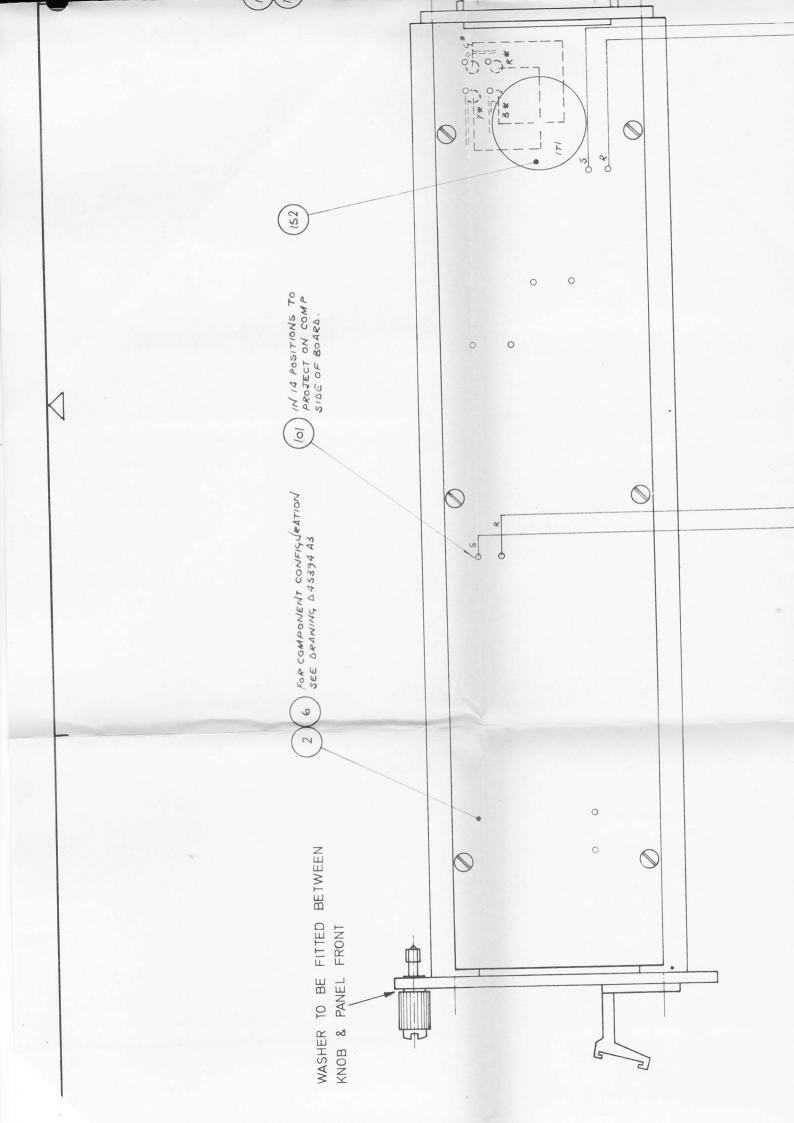

- 1 ASSEMBLY TO BE IN ACCORDANCE WITH DRAWING EA10484 NOTES 1,4,6,7

- 2 WIRING TO BE IN ACCORDANCE WITH DRAWINGS EA10137 NOTES & EA10139 NOTES

- 3 COMPONENTS TO BE WIRED TO PRINTED BOARD IN ACCORDANCE WITH DRAWING EA10140 NOTES 1, 4,11,13

- 4 THE COUNTERSUNK HOLES IN THE FRONT PANEL AND HANDLE MUST HAVE THE ANODISED FINISH REMOVED BEFORE ASSEMBLY

- 5. \* DENOTES EXISTING WIRE.

ALL OTHER WIRE TO BE PUNI /IM IN COLOUR SHOWN.

- 6. CODING PINS OF PLUG (ITEM 173) TO BE SET IN POSITIONS AS SHOWN PRIOR TO MOUNTING OF PLUG TO BOARD, FOR METHOD OF CODING SEE DSK 17963 44.

THIRD ANGLE PROJECTION

All dimensions in millimetres unless otherwise stated:

Normal tolerances

no decimal place:-

±1 mm

one decimal place:-

±0.3mm

two decimal places:-

±0.1mm

unless otherwise stated

±0.1mm

This drawing/specification is the property of the British Broadcasting Corporation and may not be reproduced or disclosed to a third party in any form without the written permission of the Corporation.

UN14/12

# **ASSEMBLY**

& WIRING

DRN. TCD. CKD. APPD.

k.Turner GM

DESIGNS DEPARTMENT

D 45390 A2

PARTS LIST D 45389 44 CIRCUIT D 45388 41.

TRIM BOARD TO DIMENSIONS SHOWN

TRIM BOARD TO DIMENSIONS SHOWN